РЕЗОЛЮЦІЯ: Громадського обговорення навчальної програми статевого виховання

ЧОМУ ФОНД ОЛЕНИ ПІНЧУК І МОЗ УКРАЇНИ ПРОПАГУЮТЬ "СЕКСУАЛЬНІ УРОКИ"

ЕКЗИСТЕНЦІЙНО-ПСИХОЛОГІЧНІ ОСНОВИ ПОРУШЕННЯ СТАТЕВОЇ ІДЕНТИЧНОСТІ ПІДЛІТКІВ

Батьківський, громадянський рух в Україні закликає МОН зупинити тотальну сексуалізацію дітей і підлітків

Відкрите звернення Міністру освіти й науки України - Гриневич Лілії Михайлівні

Представництво українського жіноцтва в ООН: низький рівень культури спілкування в соціальних мережах

Гендерна антидискримінаційна експертиза може зробити нас моральними рабами

ЛІВИЙ МАРКСИЗМ У НОВИХ ПІДРУЧНИКАХ ДЛЯ ШКОЛЯРІВ

ВІДКРИТА ЗАЯВА на підтримку позиції Ганни Турчинової та права кожної людини на свободу думки, світогляду та вираження поглядів

- Гідрологія і Гідрометрія

- Господарське право

- Економіка будівництва

- Економіка природокористування

- Економічна теорія

- Земельне право

- Історія України

- Кримінально виконавче право

- Медична радіологія

- Методи аналізу

- Міжнародне приватне право

- Міжнародний маркетинг

- Основи екології

- Предмет Політологія

- Соціальне страхування

- Технічні засоби організації дорожнього руху

- Товарознавство продовольчих товарів

Тлумачний словник

Авто

Автоматизація

Архітектура

Астрономія

Аудит

Біологія

Будівництво

Бухгалтерія

Винахідництво

Виробництво

Військова справа

Генетика

Географія

Геологія

Господарство

Держава

Дім

Екологія

Економетрика

Економіка

Електроніка

Журналістика та ЗМІ

Зв'язок

Іноземні мови

Інформатика

Історія

Комп'ютери

Креслення

Кулінарія

Культура

Лексикологія

Література

Логіка

Маркетинг

Математика

Машинобудування

Медицина

Менеджмент

Метали і Зварювання

Механіка

Мистецтво

Музика

Населення

Освіта

Охорона безпеки життя

Охорона Праці

Педагогіка

Політика

Право

Програмування

Промисловість

Психологія

Радіо

Регилия

Соціологія

Спорт

Стандартизація

Технології

Торгівля

Туризм

Фізика

Фізіологія

Філософія

Фінанси

Хімія

Юриспунденкция

Тригери

Тригером називають пристрій, що має два стійких стани рівноваги і здатний стрибком переходити з одного стану стійкої рівноваги в інший під дією зовнішнього (керувального) сигналу запуску.

Тригер можна умовно розглядати як окремий випадок релаксаційного генератора в очікувальному режимі. Спільним для них є наявність глибокого позитивного 33 та ключовий режим роботи активних елементів зі стрибкоподібним переходом їх із закритого стану відсікання у відкритий стан насичення, а відмітним є те, що тривалість знаходження в обох станах рівноваги для тригера визначається лише часом надходження керувальних імпульсів. Тригер не має власних часозадавальних елементів, його параметри не визначаються ні тривалістю перебування в стані стійкої рівноваги, ні періодичністю зміни цього стану.

Тригери використовують як формувачі прямокутних імпульсів, дискримінатори, елементи затримки сигналів тощо. Проте основним їх призначенням є побудова елементів електронної пам'яті. Кожен тригер здатний запам'ятати один біт інформації, але їх можна об'єднувати в регістри, лічильники, перерахункові декади тощо.

Тригери можуть бути побудовані на дискретних електронних або магнітних елементах, ОП, логічних елементах. Промисловість випускає різноманітні тригерні, регістрові, лічильні та інші мікросхеми, побудовані на тригерах.

Схеми тригерів різняться способом запису інформації, кількістю ступенів у складі тригера, логікою роботи.

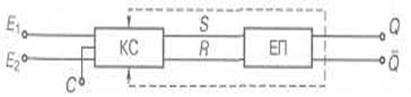

Структурно тригер (рис. 7.15) можна розглядати як поєднання елемента пам'яті (ЕП) та керувальної схеми (КС).

Рис. 7.15. Спрощена структурна схема тригера

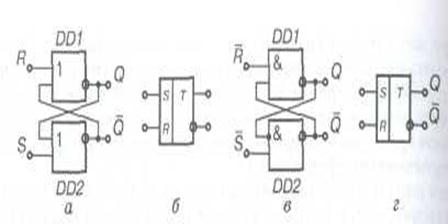

Рис. 7.16. Структурні схеми (а, в) й умовні графічні позначення (б, г) найпростіших

асинхронних тригерів, побудованих на базових логічних елементах.

Елемент пам'яті – це чотириполюсник з двома інформаційними входами S (set – установлення) й R (reset – скидання) і двома виходами прямим Q й інверсним  , сигнали на яких мають завжди протилежні значення. Перемикальний сигнал 1 на вході S установлює ЕП в стан 1 на виході Q, а сигнал 1 на вході R – у стан 0. Основному (початковому) стану тригера відповідає наявність стану 0 на виході Q.

, сигнали на яких мають завжди протилежні значення. Перемикальний сигнал 1 на вході S установлює ЕП в стан 1 на виході Q, а сигнал 1 на вході R – у стан 0. Основному (початковому) стану тригера відповідає наявність стану 0 на виході Q.

У загальному випадку ЕП може мати додаткові входи встановлення.

Розглянутий ЕП називають асинхроним RS-тригером. Стан цього тригера визначається в кожний момент часу станами його входів, тобто зміна сигналу на вході відразу передається на вихід тригера.

Керувальна схема перетворює інформацію Е1 та Е2, що надходить на її входи, на робочі сигнали входів установлення тригера. В деяких випадках сигнали з виходу тригера подають на вхід КС. В найпростішому випадку КС може бути відсутньою й асинхронним ЕП керують його власні вихідні сигнали. При цьому вихід першого елемента з'єднують з одним із входів другого, а вхід другого – з одним із входів першого. Таким чином утворюють позитивні 33, що забезпечують стійкі стани схеми (рис. 7.16). Тригери потенціальної системи елементів, які мають ще один вхід – синхронізуючий (С), називають синхронними (рис. 7.17). Імпульси, що надходять на цей вхід, визначають момент сприйняття тригером інформації. Ці імпульси виробляються генератором опорних сигналів і використовують для узгодження в часі іроботи окремих елементів цифрового пристрою. Будь-яка інформація може бути записана в синхронний тригер тільки за наявності синхроімпульсу.

Рис. 7.17. Структурні схеми (а, в) й умовні графічні позначення (б, г) синхронних

тригерів

Синхронні тригери можна використовувати також в асинхронному режимі Для цього досить на вхід С подати постійну напругу, що відповідає амплітуді синхроімпульсу.

За кількістю ступенів тригери поділяються на одно-, двоступеневі тощо, у двоступеневих тригерах створюється ефект затримки інформації. їх ще називають MS-тригерами (master-slave), оскільки другий ступінь (slave) цього тригера повторює стан першого (master).

У пристроях цифрової техніки застосовуються тригери з різними типами логіки функціонування: з запуском установлення (RS-тригер); із затримкою (D-тригер); із лічильним входом (T-тригер); універсальний (JK-тригер) та ін. Крім того, для відтворення форми спотворених прямокутних імпульсів і формування прямокутних імпульсів з сигналів довільної форми (наприклад, близьких до гармонічних) використовують спеціальні тригери Шмітта.

Принцип дії того чи іншого тригера можна описати за допомогою таблиць переходів, характеристичних рівнянь логічних функцій, часових діаграм або графіків. Скористаємось таблицями переходів, тобто таблицями інформаційних значень станів сигналів (0 чи 1) на вході й виході тригера, а іноді – станів його внутрішніх елементів.

Асинхронний RS-тригер є найпростішим. Крім самостійного застосування, він входить до складу тригерів інших типів. На рис. 7.16, а, 6 показано логічну структуру й умовне графічне позначення цього тригера, побудованого на двох логічних елементах АБО – НЕ. Його нульовому початковому стану відповілає рівень 0 сигналів на входах R та S і рівень 0 сигналу на виході Q, оскільки для елементів АБО – НЕ рівні логічного нуля пасивні. Перемикання тригера з одного стійкого стану в інший відбувається при дії. активних сигналів з рівнем і на входах. Під дією сигналу рівня R = 1 елемент DD1 установлюється в стан, при якому на його виході Q буде Q = 0, тобто дія активного сигналу на вході R не змінює нульового стану тригера.

Зміна стану тригера під дією сигналу рівня R =1 відбудеться лише тоді, коли тригер знаходиться в стані 1. Під дією сигналу рівня S = 1 елемент DD2 встановлюється в стан, при якому на його виході буде Q=1. Одночасна подача сигналів активного рівня (1) на входи R та S недопустима, оскільки в цьому разі на обох виходах установлюється сигнал рівня 0, а після зняття сигналів активного рівня з входів стан тригера буде невизначеним.

У таблиці станів (табл. 7.1) знаком × позначено стан, що відповідає недопустимій комбінації рівнів вхідних сигналів.

Логічну структуру й умовне графічне позначення тригера, побудова-ного на двох логічних елементах І – НЕ, зображено на рис. 7.1б, в, г. Цей тригер називають RS-тригером з інверсними входами, тому що внаслідок дії на його вході сигналу рівня 0 на основному виході Q буде сигнал рівня 1. Отже, активним логічним рівнем сигналів на входах тригера в цьому разі є рівень логічного нуля, а пасивним – рівень логічної одиниці. Входи такого тригера позначають інверсіями  та

та  .

.

Таблиця 7.1

| Вхід | Вихід | Режим роботи тригера | |||

| АБО — НЕ | І —НЕ | Q |

| ||

| S | R |

|

| ||

| Попередній стан 1 0 0 1 × × | Зберігання інформації Запис 1 Запис 0 Заборонений режим |

Якщо застосувати позначення входів цього тригера інверсіями, то таблиця його станів буде такою самою, як і для тригера на елементах АБО – НЕ (табл. 7.1).

На рис. 7.17, а, б показано логічну структуру й умовне графічне позначення синхронного RS-тригера. Він складається з асинхронного RS-тригера, на входах якого є логічні елементи І або І – НЕ. Вони забезпечують передачу сигналів активного рівня з інформаційних входів S і R синхронного тригера на входи  та

та  асинхронного тригера тільки за наявності сигналів рівня 1 на вході синхронізації С. Якщо ж на цьому вході є сигнали рівня 0, то на входи асинхронного тригера вони не передаються і він зберігає встановлений раніше стан. Логічні переходи в синхронному RS-тригері наведено в табл. 7.2.

асинхронного тригера тільки за наявності сигналів рівня 1 на вході синхронізації С. Якщо ж на цьому вході є сигнали рівня 0, то на входи асинхронного тригера вони не передаються і він зберігає встановлений раніше стан. Логічні переходи в синхронному RS-тригері наведено в табл. 7.2.

D-тригер (рис. 7.17, в, г) має тільки один логічний вхід D (delay – затримка). Такий тригер легко дістати з синхронного RS-тригера, якщо на його вхід R подати сигнал 33 із входу  елемента DD3. В цьому разі передача інформації з входу DD3, що відповідає входу S синхронного RS-тригера, на вихід Q відбувається тільки при дії синхроімпульсу. Якщо сигнал па вході R змінився за відсутності синхроімпульсу, то стан тригера на виході Q зберігається і змінюється лише після подачі наступного синхроімпульсу, тобто відбувається затримка передачі інформації на час, який дорівнює періоду синхроімпульсів. Логічні переходи D-тригера наведено з табл. 7.3.

елемента DD3. В цьому разі передача інформації з входу DD3, що відповідає входу S синхронного RS-тригера, на вихід Q відбувається тільки при дії синхроімпульсу. Якщо сигнал па вході R змінився за відсутності синхроімпульсу, то стан тригера на виході Q зберігається і змінюється лише після подачі наступного синхроімпульсу, тобто відбувається затримка передачі інформації на час, який дорівнює періоду синхроімпульсів. Логічні переходи D-тригера наведено з табл. 7.3.

Таблиця 7.2

| Вхід | Вихід | Режим роботи тригера | |||

| S | R | C | Q |

| |

| - - - - - * | - - - - - * | Попередній стан Запис 1 Запис 0 Заборонений режим |

Таблиця 7.3

| Вхід | Вихід | Режим роботи тригера | ||

| D | C | Q |

| |

| - - | - - | Зберігання інформації Запис 0 Запис 1 |

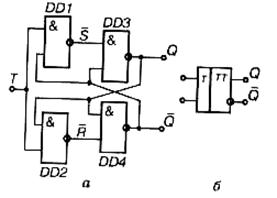

Т-тригер має теж один вхід Т (рис. 7.18, а, б). Якщо на цей вхід подано сигнал, рівень якого відповідає логічній одиниці, то після кожного імпульсу тригер переходить у протилежний стан, а коли рівень сигналу на вході відповідає логічному нулю тригер залишається в попередньому стані. Таким чином, Т-тригер виконує лічбу за модулем два (як однорозрядний лічильник у двійковому коді).

Т-тригер можна дістати з синхронного RS-тригера введенням в нього двох додаткових 33 між входом S і виходом  та між входом R і виходом Q. Тригер можна також утворити з D-тригера, якщо з'єднати його вихід

та між входом R і виходом Q. Тригер можна також утворити з D-тригера, якщо з'єднати його вихід  і вхід D.

і вхід D.

Усі розглянуті та деякі інші типи тригерів можна реалізувати за допомогою універсального JK-тригера, що працює за одно- або двоступеневою схемою.

Двоступеневий JK-тригер (рис 7.19) складаться з двох послідовно з'єднаних частин, до складу кожної з яких входить асинхронний RS-eлeмент пам'яті та КС на тривходових базових елементах І - НЕ. Особливість його схеми полягає в тому, що вона охоплена колами позитивного 33 виходів Q і  з входами першої КС (КС1) і має кола прямої передачі сигналу з виходів першої КС на входи другої (КС2). Кола позитивного 33 забезпечують зміну стану всієї схе ми а кола прямої передачі сигналу відокремлюють перший ступінь схеми від другого при надходженні переднього фронту синхроімпуль-су, забезпечуючи передачу стану першого ЕП у другий при дії заднього фронту цього імпульсу. Таким чином, інформація з входу спочатку записується в перший ступінь тригера (ЕП1), а потім передається в другий (ЕП2).

з входами першої КС (КС1) і має кола прямої передачі сигналу з виходів першої КС на входи другої (КС2). Кола позитивного 33 забезпечують зміну стану всієї схе ми а кола прямої передачі сигналу відокремлюють перший ступінь схеми від другого при надходженні переднього фронту синхроімпуль-су, забезпечуючи передачу стану першого ЕП у другий при дії заднього фронту цього імпульсу. Таким чином, інформація з входу спочатку записується в перший ступінь тригера (ЕП1), а потім передається в другий (ЕП2).

Рис. 7.18. Структурна схема (а) й умовне графічне позначення (б) Т-тригера (таймера)

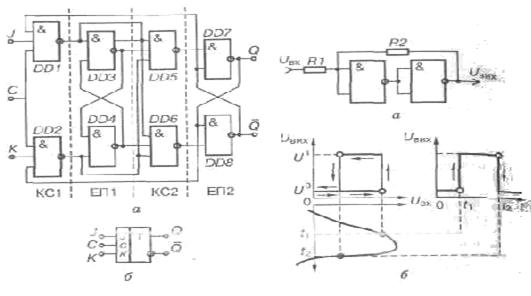

Рис. 7.19. Структурна схема (а) й умовне Рис. 7.20. Тригер Шмітта (а) і

і графічне позначення Т-тригера (таймера) діаграми (б), що ілюструють його

роботу

JК-тригер називають універсальним і тому, що його можна легко (практично без додаткових елементів) перетворити на тригер, який діє відповідно до логіки будь-якого з розглянутих тригерів.

Тригер Шмітта застосовується для формування прямокутних імпульсів з коливань довільної форми. Цей тригер, структурну схему якого зображено на рис. 7.20, а, утворюють із двох інверторів, з'єднаних послідовно (щоб забезпечити умову балансу фаз), охоплених частотонеза-лежним позитивним 33 через резистор R2. Завдяки сильному такому зв'язку АХ тригера має вигляд майже прямокутної гістерезисної петлі (рис. 7.20, 6), ширина якої

. (7.36)

. (7.36)

де Uвмик та Uвим – порогові вхідні напруги, яким відповідають напруги рівнів логічно одиниці U1вих і логічного нуля U°вих на виході схеми.

Якщо тригер Шмітта складають із базових логічних елементів на мікросхемах серії К155, то R1, < 470 Ом, a R2 < 2,2кОм. У кожній серії мікросхем розроблено кілька різновидів тригерів Шмітта.

Читайте також:

- D - тригери

- R-S - тригери

- R-S-тригери.

- RS – тригери

- Поняття про тригери в системі SQL Server.

- Симетричні тригери на біполярних транзисторах.

- Синхронізуємі RS-тригери.

- Синхронні тригери.

- ТРИГЕРИ

- Тригери на польових транзисторах.

- Тригери типу JK

| <== попередня сторінка | | | наступна сторінка ==> |

| Генератори релаксаційних коливань | | | Розділ 3РАДІОЕЛЕКТРОННІ ПРИСТРОЇ ТА СИСТЕМИ |

|

Не знайшли потрібну інформацію? Скористайтесь пошуком google: |

© studopedia.com.ua При використанні або копіюванні матеріалів пряме посилання на сайт обов'язкове. |