РЕЗОЛЮЦІЯ: Громадського обговорення навчальної програми статевого виховання

ЧОМУ ФОНД ОЛЕНИ ПІНЧУК І МОЗ УКРАЇНИ ПРОПАГУЮТЬ "СЕКСУАЛЬНІ УРОКИ"

ЕКЗИСТЕНЦІЙНО-ПСИХОЛОГІЧНІ ОСНОВИ ПОРУШЕННЯ СТАТЕВОЇ ІДЕНТИЧНОСТІ ПІДЛІТКІВ

Батьківський, громадянський рух в Україні закликає МОН зупинити тотальну сексуалізацію дітей і підлітків

Відкрите звернення Міністру освіти й науки України - Гриневич Лілії Михайлівні

Представництво українського жіноцтва в ООН: низький рівень культури спілкування в соціальних мережах

Гендерна антидискримінаційна експертиза може зробити нас моральними рабами

ЛІВИЙ МАРКСИЗМ У НОВИХ ПІДРУЧНИКАХ ДЛЯ ШКОЛЯРІВ

ВІДКРИТА ЗАЯВА на підтримку позиції Ганни Турчинової та права кожної людини на свободу думки, світогляду та вираження поглядів

- Гідрологія і Гідрометрія

- Господарське право

- Економіка будівництва

- Економіка природокористування

- Економічна теорія

- Земельне право

- Історія України

- Кримінально виконавче право

- Медична радіологія

- Методи аналізу

- Міжнародне приватне право

- Міжнародний маркетинг

- Основи екології

- Предмет Політологія

- Соціальне страхування

- Технічні засоби організації дорожнього руху

- Товарознавство продовольчих товарів

Тлумачний словник

Авто

Автоматизація

Архітектура

Астрономія

Аудит

Біологія

Будівництво

Бухгалтерія

Винахідництво

Виробництво

Військова справа

Генетика

Географія

Геологія

Господарство

Держава

Дім

Екологія

Економетрика

Економіка

Електроніка

Журналістика та ЗМІ

Зв'язок

Іноземні мови

Інформатика

Історія

Комп'ютери

Креслення

Кулінарія

Культура

Лексикологія

Література

Логіка

Маркетинг

Математика

Машинобудування

Медицина

Менеджмент

Метали і Зварювання

Механіка

Мистецтво

Музика

Населення

Освіта

Охорона безпеки життя

Охорона Праці

Педагогіка

Політика

Право

Програмування

Промисловість

Психологія

Радіо

Регилия

Соціологія

Спорт

Стандартизація

Технології

Торгівля

Туризм

Фізика

Фізіологія

Філософія

Фінанси

Хімія

Юриспунденкция

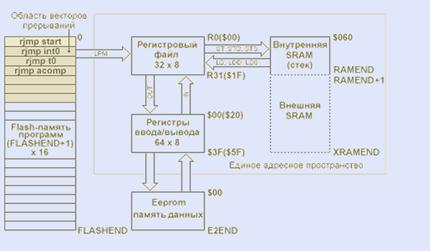

Адресация памяти и ввода-вывода. Циклы обмена между процессором и памятью.

Под адресацией подразумевается способ, с помощью которого адресуется информация, содержащаяся в памяти. Наименьшая единица информации, к которой можно адресоваться, называется адресной единицей. Каждой адресуемой в памяти единице присваивается единственный признак - адрес. Каждая адресная единица имеет свой адрес. Адрес устанавливается для каждого места хранения информации и не зависит от содержания записей. Другими словами запоминающее устройство - это совокупность регистров определенной длины. Каждому регистру присвоен адрес. Для вызова из памяти содержимого такого регистра или записи в регистр какой-либо информации необходимо указать его адрес. Длина каждого регистра есть в этом случае наименьшая адресуемая единица информации.

ВРегистрами РІРІРѕРґР°/вывода являются регистры SREG, MCUSR Рё указатель стека SPH:SPL Р° также регистры, управляющие системой прерывания микроконтроллера, режимами подключения EEPROM памяти, сторожевым таймером, портами РІРІРѕРґР°/вывода Рё РґСЂСѓРіРёРјРё периферийными узлами. Р’СЃРµ регистры РІРІРѕРґР°/вывода РјРѕРіСѓС‚ считываться Рё записываться через РРћРќ (POH — регистры общего назначения) РїСЂРё помощи команд IN, OUT Регистры РІРІРѕРґР°/вывода, имеющие адреса РІ диапазоне $00 - $1F (знак $ указывает РЅР° шестнадцатеричную систему счисления), обладают возможностью побитовой адресации. Непосредственная установка Рё СЃР±СЂРѕСЃ отдельных разрядов этих регистров выполняется командами SBI Рё CBI Для признаков результата операции, которые являются битами регистра РІРІРѕРґР°/вывода SREG, имеется целый набор команд установки Рё СЃР±СЂРѕСЃР°. Команды условных переходов РІ качестве СЃРІРѕРёС… операндов РјРѕРіСѓС‚ иметь как биты-признаки результата операции, так Рё отдельные разряды побитно адресуемых регистров РІРІРѕРґР°/вывода. РќР° СЂРёСЃ. 2.3 показано распределение адресов РІ едином адресном пространстве.

ВМладшие 32 адреса ($0 - $1F) соответствуют оперативным регистрам С‚.Рµ. РРћРќ. Следующие 64 адреса ($20 - $5F) зарезервированы для регистров РІРІРѕРґР°/вывода. Внутренняя SRAM Сѓ всех AVR начинается СЃ адреса $60. Таким образом, регистры РІРІРѕРґР°/вывода имеют РґРІРѕР№РЅСѓСЋ нумерацию. Если используются команды IN, OUT, SBI, CBI, SBIC, SBIS, то следует использовать нумерацию регистров РІРІРѕРґР°/вывода, начинающуюся СЃ нуля (назовем ее РѕСЃРЅРѕРІРЅРѕР№). Если же Рє регистрам РІРІРѕРґР°/вывода доступ осуществляется как Рє ячейкам памяти, то необходимо использовать нумерацию единого адресного пространства оперативной памяти данных AVR. Очевидно, что адрес РІ едином адресном пространстве памяти данных получается путем прибавления числа $20 Рє РѕСЃРЅРѕРІРЅРѕРјСѓ адресу регистра РІРІРѕРґР°/вывода. Для хранения оперативных данных программист, РєСЂРѕРјРµ РРћРќ, может использовать внутреннюю Рё внешнюю (если РѕРЅРё имеются) блоки SRAM (СЃРј. СЂРёСЃ. 2.3). РРёСЃ. 2.3. Программная модель AVR-микроконтроллеров. Работа СЃ внешней SRAM может быть программно разрешена/запрещена установкой/СЃР±СЂРѕСЃРѕРј бита SRE РІ регистре РІРІРѕРґР°/вывода MCUSR. Операции обмена СЃ внутренней оперативной памятью AVR-микроконтроллер выполняет Р·Р° РґРІР° машинных цикла. Доступ Рє внешней SRAM требует РѕРґРЅРѕРіРѕ дополнительного цикла РЅР° каждый байт РїРѕ сравнению СЃ внутренней памятью. РљСЂРѕРјРµ того, установкой бита SRW РІ регистре РІРІРѕРґР°/вывода MCUSR можно программно увеличить время обмена СЃ внешней SRAM еще РЅР° РѕРґРёРЅ дополнительный машинный цикл ожидания. Выполнять арифметико-логические операции Рё операции СЃРґРІРёРіР° непосредственно над содержимым ячеек памяти нельзя. Нельзя также записать константу или очистить содержимое ячейки памяти. Система команд AVR позволяет лишь выполнять операции обмена данными между ячейками SRAM Рё оперативными регистрами. Достоинством системы команд можно считать разнообразные режимы адресации ячеек памяти. РљСЂРѕРјРµ РїСЂСЏРјРѕР№ адресации имеются следующие режимы: косвенная, косвенная СЃ РїРѕСЃС‚-инкрементом, косвенная СЃ РїСЂРµ-декрементом Рё косвенная СЃРѕ смещением. Поскольку внутренняя Рё внешняя SRAM РІС…РѕРґСЏС‚ РІ единое адресное пространство (вместе СЃ оперативными регистрами Рё регистрами РІРІРѕРґР°/вывода), то для доступа Рє ячейкам внутренней Рё внешней памяти используются РѕРґРЅРё Рё те же команды. Следует отметить, что регистры РІРІРѕРґР°/вывода РЅРµ полностью используют отведенные для РЅРёС… 64 адреса. Неиспользуемые адреса зарезервированы для будущих применений, дополнительных ячеек памяти РїРѕ этим адресам РЅРµ существует.

ВМладшие 32 адреса ($0 - $1F) соответствуют оперативным регистрам С‚.Рµ. РРћРќ. Следующие 64 адреса ($20 - $5F) зарезервированы для регистров РІРІРѕРґР°/вывода. Внутренняя SRAM Сѓ всех AVR начинается СЃ адреса $60. Таким образом, регистры РІРІРѕРґР°/вывода имеют РґРІРѕР№РЅСѓСЋ нумерацию. Если используются команды IN, OUT, SBI, CBI, SBIC, SBIS, то следует использовать нумерацию регистров РІРІРѕРґР°/вывода, начинающуюся СЃ нуля (назовем ее РѕСЃРЅРѕРІРЅРѕР№). Если же Рє регистрам РІРІРѕРґР°/вывода доступ осуществляется как Рє ячейкам памяти, то необходимо использовать нумерацию единого адресного пространства оперативной памяти данных AVR. Очевидно, что адрес РІ едином адресном пространстве памяти данных получается путем прибавления числа $20 Рє РѕСЃРЅРѕРІРЅРѕРјСѓ адресу регистра РІРІРѕРґР°/вывода. Для хранения оперативных данных программист, РєСЂРѕРјРµ РРћРќ, может использовать внутреннюю Рё внешнюю (если РѕРЅРё имеются) блоки SRAM (СЃРј. СЂРёСЃ. 2.3). РРёСЃ. 2.3. Программная модель AVR-микроконтроллеров. Работа СЃ внешней SRAM может быть программно разрешена/запрещена установкой/СЃР±СЂРѕСЃРѕРј бита SRE РІ регистре РІРІРѕРґР°/вывода MCUSR. Операции обмена СЃ внутренней оперативной памятью AVR-микроконтроллер выполняет Р·Р° РґРІР° машинных цикла. Доступ Рє внешней SRAM требует РѕРґРЅРѕРіРѕ дополнительного цикла РЅР° каждый байт РїРѕ сравнению СЃ внутренней памятью. РљСЂРѕРјРµ того, установкой бита SRW РІ регистре РІРІРѕРґР°/вывода MCUSR можно программно увеличить время обмена СЃ внешней SRAM еще РЅР° РѕРґРёРЅ дополнительный машинный цикл ожидания. Выполнять арифметико-логические операции Рё операции СЃРґРІРёРіР° непосредственно над содержимым ячеек памяти нельзя. Нельзя также записать константу или очистить содержимое ячейки памяти. Система команд AVR позволяет лишь выполнять операции обмена данными между ячейками SRAM Рё оперативными регистрами. Достоинством системы команд можно считать разнообразные режимы адресации ячеек памяти. РљСЂРѕРјРµ РїСЂСЏРјРѕР№ адресации имеются следующие режимы: косвенная, косвенная СЃ РїРѕСЃС‚-инкрементом, косвенная СЃ РїСЂРµ-декрементом Рё косвенная СЃРѕ смещением. Поскольку внутренняя Рё внешняя SRAM РІС…РѕРґСЏС‚ РІ единое адресное пространство (вместе СЃ оперативными регистрами Рё регистрами РІРІРѕРґР°/вывода), то для доступа Рє ячейкам внутренней Рё внешней памяти используются РѕРґРЅРё Рё те же команды. Следует отметить, что регистры РІРІРѕРґР°/вывода РЅРµ полностью используют отведенные для РЅРёС… 64 адреса. Неиспользуемые адреса зарезервированы для будущих применений, дополнительных ячеек памяти РїРѕ этим адресам РЅРµ существует.

Читайте також:

| <== попередня сторінка | | | наступна сторінка ==> |

| Особенности состава команд Intel. | | |

|

Не знайшли потрібну інформацію? Скористайтесь пошуком google: |

© studopedia.com.ua При використанні або копіюванні матеріалів пряме посилання на сайт обов'язкове. |