РЕЗОЛЮЦІЯ: Громадського обговорення навчальної програми статевого виховання

ЧОМУ ФОНД ОЛЕНИ ПІНЧУК І МОЗ УКРАЇНИ ПРОПАГУЮТЬ "СЕКСУАЛЬНІ УРОКИ"

ЕКЗИСТЕНЦІЙНО-ПСИХОЛОГІЧНІ ОСНОВИ ПОРУШЕННЯ СТАТЕВОЇ ІДЕНТИЧНОСТІ ПІДЛІТКІВ

Батьківський, громадянський рух в Україні закликає МОН зупинити тотальну сексуалізацію дітей і підлітків

Відкрите звернення Міністру освіти й науки України - Гриневич Лілії Михайлівні

Представництво українського жіноцтва в ООН: низький рівень культури спілкування в соціальних мережах

Гендерна антидискримінаційна експертиза може зробити нас моральними рабами

ЛІВИЙ МАРКСИЗМ У НОВИХ ПІДРУЧНИКАХ ДЛЯ ШКОЛЯРІВ

ВІДКРИТА ЗАЯВА на підтримку позиції Ганни Турчинової та права кожної людини на свободу думки, світогляду та вираження поглядів

- Гідрологія і Гідрометрія

- Господарське право

- Економіка будівництва

- Економіка природокористування

- Економічна теорія

- Земельне право

- Історія України

- Кримінально виконавче право

- Медична радіологія

- Методи аналізу

- Міжнародне приватне право

- Міжнародний маркетинг

- Основи екології

- Предмет Політологія

- Соціальне страхування

- Технічні засоби організації дорожнього руху

- Товарознавство продовольчих товарів

Тлумачний словник

Авто

Автоматизація

Архітектура

Астрономія

Аудит

Біологія

Будівництво

Бухгалтерія

Винахідництво

Виробництво

Військова справа

Генетика

Географія

Геологія

Господарство

Держава

Дім

Екологія

Економетрика

Економіка

Електроніка

Журналістика та ЗМІ

Зв'язок

Іноземні мови

Інформатика

Історія

Комп'ютери

Креслення

Кулінарія

Культура

Лексикологія

Література

Логіка

Маркетинг

Математика

Машинобудування

Медицина

Менеджмент

Метали і Зварювання

Механіка

Мистецтво

Музика

Населення

Освіта

Охорона безпеки життя

Охорона Праці

Педагогіка

Політика

Право

Програмування

Промисловість

Психологія

Радіо

Регилия

Соціологія

Спорт

Стандартизація

Технології

Торгівля

Туризм

Фізика

Фізіологія

Філософія

Фінанси

Хімія

Юриспунденкция

Tаблиця 8.2

Значення частоти тактового сигналу SCK

| SPR1 | SPR2 | Частота сигналу SCK |

| FCLK/4 | ||

| FCLK/16 | ||

| FCLK/64 | ||

| FCLK/128 |

SPI Status Register (SPSR)

| Біт $0E($2E) R/W Поч.знач. | SPCR | ||||||||

| SPIF | WCOL | - | - | - | - | - | - | ||

| R | R | R | R | R | R | R | R | ||

Рис. 8.3 - Регістр стану SPI (SPSR)

Біт 7 - SPIF (SPI Interrupt Flag). Прапорець переривання від SPI. Встановлюється в «1» по закінченні передачі чергового байта, а також при переводі мікроконтролера з режиму Master в режим Slave за допомогою виводу SS (див. розділ 3.3). Прапорець скидається апаратно або при старті підпрограми обробки переривання, або після читання регістра стану SPI з наступним звертанням до регістра даних SPDR.

Біт 6 - WCOL (Write Collision Flag). Прапорець конфлікту запису. Установлюється в «1» при спробі запису в регістр даних SPDR під час передачі чергового байта. Прапорець скидається апаратно після читання регістра стану SPI з наступним звертанням до регістра даних SPI.

Біти 5...0 - зарезервовані, читаються як «0».

SPI Data Register (SPDR)

| Біт $0F ($2F) R/W Поч.знач. | SPDR | ||||||||

| MSB | - | - | - | - | - | - | LSB | ||

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | ||

Рис. 8.4 - Регістр введення - виведення SPI (SPDR)

Передані дані записуються, а прийняті - зчитуються з регістра даних SPDR, розташованого за адресою $0F ($2F). Запис у цей регістр ініціює початок передачі, а при його читанні зчитується вміст прийомного буфера регістра зсуву. Тому цей регістр можна назвати буфером між регістровим файлом мікроконтролера й регістром зсуву модуля SPI.

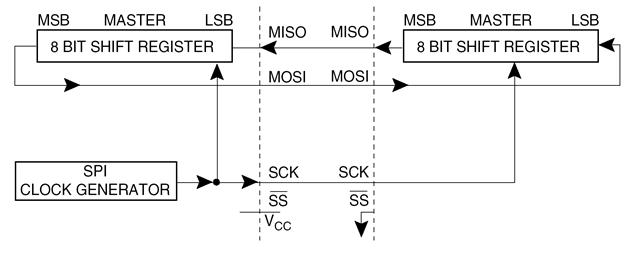

З'єднання двох мікроконтролерів (ведучий ведений) по інтерфейсу SPI показано на мал.8.5. Вивід SCK ведучого мікроконтролера є виходом тактового сигналу, а веденого мікроконтролера - входом.

Рис. 8.5 - З'єднання мікроконтролерів за інтерфейсом SPI

Передача даних здійснюється наступним чином. При записі в регістр даних SPI ведучого мікроконтролера запускається генератор тактового сигналу модуля SPI, і дані починають порозрядно видаватися на вивід MOSI і, відповідно, надходити па вивід MOSI веденого мікроконтролера. Після видачі останнього розряду поточного байта генератор тактового сигналу зупиняється з одночасною установкою в «1» прапорця «Кінець передачі» (SPIF). Якщо переривання від модуля SPI дозволено (прапорець SPIE регістра SPCR установлений в «1»), генерується запит на переривання. При підключенні до ведучого пристрою декількох ведених, що дозволено специфікацією SPI, вибір конкретного веденого пристрою здійснюється подачею на його вхід SS сигналу НИЗЬКОГО рівня.

Образно кажучи, два регістри зсуву веденого й ведучого пристроїв можна вважати одним розподіленим 16-розрядним циклічним регістром зсуву, як показано на рис.8.5. Одночасно з передачею даних від ведучого до веденого відбувається передача й у зворотному напрямку. Таким чином, у кожному циклі зсуву відбувається обмін даними між пристроями.

У модулі використовується одинарна буферизація при передачі й подвійна - при прийманні. Це означає, що готовий для передачі байт даних не може бути записаний у регістр даних SPI до закінчення попереднього циклу обміну. При спробі змінити вміст регістра даних під час передачі встановлюється в «1» прапорець WCOL регістра SPSR. Скидається цей прапорець після читання регістра SPSR з наступним звертанням до регістра даних SPI.

Відповідно під час прийому прийнятий байт повинен бути прочитаний з регістра даних SPI до того, як у регістр зсуву надійде останній розряд наступного байта. У противному випадку перший байт буде загублений.

Читайте також:

| <== попередня сторінка | | | наступна сторінка ==> |

| Tаблиця 8.1 | | | Режими передачі даних |

|

Не знайшли потрібну інформацію? Скористайтесь пошуком google: |

© studopedia.com.ua При використанні або копіюванні матеріалів пряме посилання на сайт обов'язкове. |