РЕЗОЛЮЦІЯ: Громадського обговорення навчальної програми статевого виховання

ЧОМУ ФОНД ОЛЕНИ ПІНЧУК І МОЗ УКРАЇНИ ПРОПАГУЮТЬ "СЕКСУАЛЬНІ УРОКИ"

ЕКЗИСТЕНЦІЙНО-ПСИХОЛОГІЧНІ ОСНОВИ ПОРУШЕННЯ СТАТЕВОЇ ІДЕНТИЧНОСТІ ПІДЛІТКІВ

Батьківський, громадянський рух в Україні закликає МОН зупинити тотальну сексуалізацію дітей і підлітків

Відкрите звернення Міністру освіти й науки України - Гриневич Лілії Михайлівні

Представництво українського жіноцтва в ООН: низький рівень культури спілкування в соціальних мережах

Гендерна антидискримінаційна експертиза може зробити нас моральними рабами

ЛІВИЙ МАРКСИЗМ У НОВИХ ПІДРУЧНИКАХ ДЛЯ ШКОЛЯРІВ

ВІДКРИТА ЗАЯВА на підтримку позиції Ганни Турчинової та права кожної людини на свободу думки, світогляду та вираження поглядів

- Гідрологія і Гідрометрія

- Господарське право

- Економіка будівництва

- Економіка природокористування

- Економічна теорія

- Земельне право

- Історія України

- Кримінально виконавче право

- Медична радіологія

- Методи аналізу

- Міжнародне приватне право

- Міжнародний маркетинг

- Основи екології

- Предмет Політологія

- Соціальне страхування

- Технічні засоби організації дорожнього руху

- Товарознавство продовольчих товарів

Тлумачний словник

Авто

Автоматизація

Архітектура

Астрономія

Аудит

Біологія

Будівництво

Бухгалтерія

Винахідництво

Виробництво

Військова справа

Генетика

Географія

Геологія

Господарство

Держава

Дім

Екологія

Економетрика

Економіка

Електроніка

Журналістика та ЗМІ

Зв'язок

Іноземні мови

Інформатика

Історія

Комп'ютери

Креслення

Кулінарія

Культура

Лексикологія

Література

Логіка

Маркетинг

Математика

Машинобудування

Медицина

Менеджмент

Метали і Зварювання

Механіка

Мистецтво

Музика

Населення

Освіта

Охорона безпеки життя

Охорона Праці

Педагогіка

Політика

Право

Програмування

Промисловість

Психологія

Радіо

Регилия

Соціологія

Спорт

Стандартизація

Технології

Торгівля

Туризм

Фізика

Фізіологія

Філософія

Фінанси

Хімія

Юриспунденкция

Логічні елементи емітерно-зв'язкової логіки

Схемотехніка елементів ЕЗЛ заснована на використанні диференціального підсилювача в режимі перемикання струму. Елементи ЕЗЛ з'явилися в 1967 р. і в цей час є самими швидкодіючими серед напівпровідникових елементів на основі кремнію. Затримки поширення сигналів в елементах ЕЗЛ зменшилися до субнаносекундного діапазону (приблизно 1 нс).

Зверхшвидкодія елементів ЕЗЛ досягається за рахунок використання ненасиченого режиму роботи транзисторів, вихідних емітерних повторювачів, малих амплітуд логічних сигналів (близько 0,8 В). У логічних елементах ЕЗЛ є парафазний вихід, що дозволяє одночасно одержувати пряме й інверсне значення реалізованої функції. Це дає помітне зниження загальної кількості мікросхем в апаратурі.

Особливостями схемотехніки ЕЗЛ і її характеристик є:

• можливість об'єднання виходів декількох елементів для утворення нових функцій;

• можливість роботи на низькоомне навантаження завдяки наявності емітерних повторювачів;

• невелике значення роботи перемикання й незалежність споживаної потужності від частоти перемикання;

• висока стабільність динамічних параметрів при зміні температури й напруги живлення;

• використання негативного джерела живлення й заземлення колекторних ланцюгів, що зменшує залежність вихідних сигналів від перешкод у шинах живлення.

До недоліків елементів ЕЗЛ відносять складність схем, значне споживання потужності й труднощі узгодження з мікросхемами ТТЛ і ТТЛШ.

Промисловість випускає ряд серій ЕЗЛ: 100, 137, 138, 187, 223, 229, 700, 500 і ДО1500.

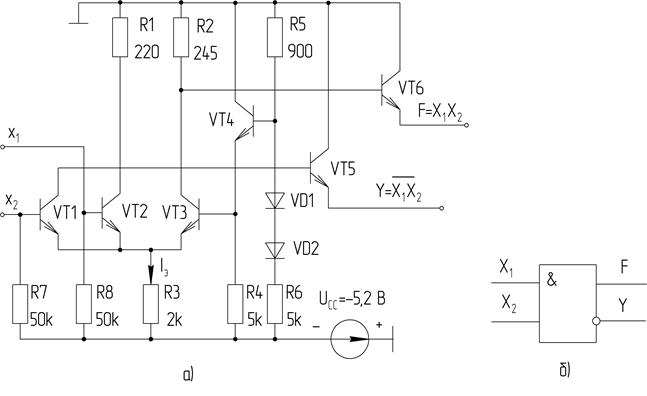

Схема типового логічного елемента ЕЗЛ серії 500 показана на рис. 3.12.

Рисунок 3.12 - Схема типового логічного елемента ЕЗЛ серії 500

Схема ЕЗЛ включає:

• перемикач струму (логічні транзистори VT1, VT2, опорний транзистор VT3, резистори R1;R2;R3);

• джерело опорного зсуву (транзистор VT4, діодиVD1,VD2резистори R5,R6);

• вигхдні емітерні повторювачі (транзистори VT5,VT6). Напруга на відкритому переході база-емітер кремнієвого транзистора є постійним параметром  В. При описі роботи елемента беруть виразу для негативної логіки: значення 0 відображається високим (з урахуванням знака) рівнем напруги

В. При описі роботи елемента беруть виразу для негативної логіки: значення 0 відображається високим (з урахуванням знака) рівнем напруги  В; значення балка. 1 відображається низьким рівнем напруги

В; значення балка. 1 відображається низьким рівнем напруги  В. Амплітуда (перепад) логічного сигналу

В. Амплітуда (перепад) логічного сигналу  В. Опорна напруга перемикача струму розташовується симетрично щодо рівнів двійкових сигналів і визначається як їх середнє:

В. Опорна напруга перемикача струму розташовується симетрично щодо рівнів двійкових сигналів і визначається як їх середнє:

В.

В.

Якщо хоча б на один із входів подана напруга  В, то даний транзистор відкривається, на нього перемикається струм IE, що створює на резисторі R1 спадання напруги мінус 0,9 У. При цьому опорний транзистор закритий і на резисторі R2 спадання напруги дорівнює мінус 0,1 У.

В, то даний транзистор відкривається, на нього перемикається струм IE, що створює на резисторі R1 спадання напруги мінус 0,9 У. При цьому опорний транзистор закритий і на резисторі R2 спадання напруги дорівнює мінус 0,1 У.

Якщо на всіх входах подані рівні UL = -1,7 У, то транзистори VТ1 і VT2 закриваються, а транзистор VT3 відкривається й на нього перемикається струм IE. У цьому випадку падіння напруги на резисторі R1 дорівнює мінус 0,1 В, а на резисторі R2 мінус 0,9 В. При цьому на колекторах лівого й правого плеча рівні напруги не відповідають прийнятому значенню двійкового сигналу. Емітерні повторювачі на транзисторах VT5 і VT6 зміщають рівні сигналів, що надходять на їхню бази з лівого й правого плеча перемикача, на  В у сторону негативних сигналів:

В у сторону негативних сигналів:  ;

;  .

.

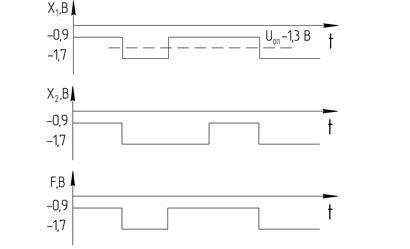

Внаслідок цього рівні вхідних і вихідних сигналів відповідають прийнятому стандарту. Тимчасові діаграми роботи елемента ЕЗЛ показані на рис. 3.13

.

Рисунок 3.13 - Часові діаграми роботи елемента ЕЗЛ

Як треба з часових діаграм, вхідні й вихідні логічні сигнали змінюються на ±0,4 В щодо опорної напруги.

У негативній логіці елемент ЕЗЛ реалізує на прямому виході F функцію І а на інверсному виході Y— функцію НІ-І, що записується як АБО-НІ. У позитивній логіці елемент ЕЗЛ реалізує функцію АБО-НІ /АБО.

Контрольні питання

До пункту 3.3.1

1) Визначення логічного елемента.

2) Логічне додавання, логічне множення, логічна інверсія.

3) Умовне графічне позначення, таблиця істинності й тимчасових діаграм елемента «АБО»,«І», «НІ»,« І-НІ»,« АБО-НІ».

До пунктів 3.3.2.1-3.3.2.6

1) Комбінована схема «І-НІ», «АБО-НІ» та ін.

2) Логічні елементи в інтегральному виконанні.

3) ДТЛ та ТТЛ (схема та принцип роботи).

4) МОП ТЛ , КМОП ТЛ, МЕП ТЛ (схема та принцип роботи).

5) Інтегрально-інжекторна логіка.

6) Логічні елементи емітерно-зв’язної логіки.

Переглядів: 1682

| <== попередня сторінка | | | наступна сторінка ==> |

| Інтегральна інжекційна логіка | | | Загальні відомості |

|

Не знайшли потрібну інформацію? Скористайтесь пошуком google: |

© studopedia.com.ua При використанні або копіюванні матеріалів пряме посилання на сайт обов'язкове. |