МАРК РЕГНЕРУС ДОСЛІДЖЕННЯ: Наскільки відрізняються діти, які виросли в одностатевих союзах

РЕЗОЛЮЦІЯ: Громадського обговорення навчальної програми статевого виховання

ЧОМУ ФОНД ОЛЕНИ ПІНЧУК І МОЗ УКРАЇНИ ПРОПАГУЮТЬ "СЕКСУАЛЬНІ УРОКИ"

ЕКЗИСТЕНЦІЙНО-ПСИХОЛОГІЧНІ ОСНОВИ ПОРУШЕННЯ СТАТЕВОЇ ІДЕНТИЧНОСТІ ПІДЛІТКІВ

Батьківський, громадянський рух в Україні закликає МОН зупинити тотальну сексуалізацію дітей і підлітків

Відкрите звернення Міністру освіти й науки України - Гриневич Лілії Михайлівні

Представництво українського жіноцтва в ООН: низький рівень культури спілкування в соціальних мережах

Гендерна антидискримінаційна експертиза може зробити нас моральними рабами

ЛІВИЙ МАРКСИЗМ У НОВИХ ПІДРУЧНИКАХ ДЛЯ ШКОЛЯРІВ

ВІДКРИТА ЗАЯВА на підтримку позиції Ганни Турчинової та права кожної людини на свободу думки, світогляду та вираження поглядів

РЕЗОЛЮЦІЯ: Громадського обговорення навчальної програми статевого виховання

ЧОМУ ФОНД ОЛЕНИ ПІНЧУК І МОЗ УКРАЇНИ ПРОПАГУЮТЬ "СЕКСУАЛЬНІ УРОКИ"

ЕКЗИСТЕНЦІЙНО-ПСИХОЛОГІЧНІ ОСНОВИ ПОРУШЕННЯ СТАТЕВОЇ ІДЕНТИЧНОСТІ ПІДЛІТКІВ

Батьківський, громадянський рух в Україні закликає МОН зупинити тотальну сексуалізацію дітей і підлітків

Відкрите звернення Міністру освіти й науки України - Гриневич Лілії Михайлівні

Представництво українського жіноцтва в ООН: низький рівень культури спілкування в соціальних мережах

Гендерна антидискримінаційна експертиза може зробити нас моральними рабами

ЛІВИЙ МАРКСИЗМ У НОВИХ ПІДРУЧНИКАХ ДЛЯ ШКОЛЯРІВ

ВІДКРИТА ЗАЯВА на підтримку позиції Ганни Турчинової та права кожної людини на свободу думки, світогляду та вираження поглядів

Контакти

- Гідрологія і Гідрометрія

- Господарське право

- Економіка будівництва

- Економіка природокористування

- Економічна теорія

- Земельне право

- Історія України

- Кримінально виконавче право

- Медична радіологія

- Методи аналізу

- Міжнародне приватне право

- Міжнародний маркетинг

- Основи екології

- Предмет Політологія

- Соціальне страхування

- Технічні засоби організації дорожнього руху

- Товарознавство продовольчих товарів

Тлумачний словник

Авто

Автоматизація

Архітектура

Астрономія

Аудит

Біологія

Будівництво

Бухгалтерія

Винахідництво

Виробництво

Військова справа

Генетика

Географія

Геологія

Господарство

Держава

Дім

Екологія

Економетрика

Економіка

Електроніка

Журналістика та ЗМІ

Зв'язок

Іноземні мови

Інформатика

Історія

Комп'ютери

Креслення

Кулінарія

Культура

Лексикологія

Література

Логіка

Маркетинг

Математика

Машинобудування

Медицина

Менеджмент

Метали і Зварювання

Механіка

Мистецтво

Музика

Населення

Освіта

Охорона безпеки життя

Охорона Праці

Педагогіка

Політика

Право

Програмування

Промисловість

Психологія

Радіо

Регилия

Соціологія

Спорт

Стандартизація

Технології

Торгівля

Туризм

Фізика

Фізіологія

Філософія

Фінанси

Хімія

Юриспунденкция

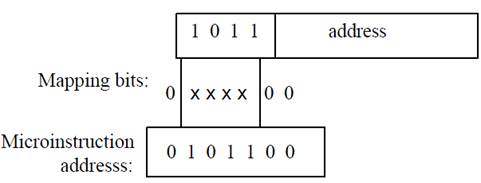

Mapping From Instruction Code To Microoperation Address

Mapping of Instruction

Branch Logic

Conditional Branching

• Status bits

– provide parameter information such as the carry-out from the adder, sign of a number, mode bits of an instruction, etc.

– control the conditional branch decisions made by the branch logic together with the field in the microinstruction that specifies a branch address.

• Branch Logic - may be implemented in one of several ways:

– The simplest way is to test the specified condition and branch if the condition is true; else increment the address register.

– This is implemented using a multiplexer:

• If the status bit is one of eight status bits, it is indicated by a 3-bit select number.

• If the select status bit is 1, the output is 0; else it is 0.

• A 1 generates the control signal for the branch; a 0 generates the signal to increment the CAR.

• Unconditional branching occurs by fixing the status bit as always being 1.

• Branching to the first word of a microprogram is a special type of branch. The branch is indicated by the opcode of the instruction.

• The mapping scheme shown in the figure allows for four microinstruction as well as overflow space from 1000000 to 1111111.

Читайте також:

- Addressing Modes

- Arithmetic Instructions

- Branch Instructions

- Computer Instructions

- Conditional Branch Instructions

- Data Transfer Instructions

- Formats of instructions

- Instruction Length

- Instructions of data handling

- Selection Of Address For Control Memory

- Symbolic Microinstructions

| <== попередня сторінка | | | наступна сторінка ==> |

| Selection Of Address For Control Memory | | | Computer Instructions |

|

Не знайшли потрібну інформацію? Скористайтесь пошуком google: |

© studopedia.com.ua При використанні або копіюванні матеріалів пряме посилання на сайт обов'язкове. |