РЕЗОЛЮЦІЯ: Громадського обговорення навчальної програми статевого виховання

ЧОМУ ФОНД ОЛЕНИ ПІНЧУК І МОЗ УКРАЇНИ ПРОПАГУЮТЬ "СЕКСУАЛЬНІ УРОКИ"

ЕКЗИСТЕНЦІЙНО-ПСИХОЛОГІЧНІ ОСНОВИ ПОРУШЕННЯ СТАТЕВОЇ ІДЕНТИЧНОСТІ ПІДЛІТКІВ

Батьківський, громадянський рух в Україні закликає МОН зупинити тотальну сексуалізацію дітей і підлітків

Відкрите звернення Міністру освіти й науки України - Гриневич Лілії Михайлівні

Представництво українського жіноцтва в ООН: низький рівень культури спілкування в соціальних мережах

Гендерна антидискримінаційна експертиза може зробити нас моральними рабами

ЛІВИЙ МАРКСИЗМ У НОВИХ ПІДРУЧНИКАХ ДЛЯ ШКОЛЯРІВ

ВІДКРИТА ЗАЯВА на підтримку позиції Ганни Турчинової та права кожної людини на свободу думки, світогляду та вираження поглядів

- Гідрологія і Гідрометрія

- Господарське право

- Економіка будівництва

- Економіка природокористування

- Економічна теорія

- Земельне право

- Історія України

- Кримінально виконавче право

- Медична радіологія

- Методи аналізу

- Міжнародне приватне право

- Міжнародний маркетинг

- Основи екології

- Предмет Політологія

- Соціальне страхування

- Технічні засоби організації дорожнього руху

- Товарознавство продовольчих товарів

Тлумачний словник

Авто

Автоматизація

Архітектура

Астрономія

Аудит

Біологія

Будівництво

Бухгалтерія

Винахідництво

Виробництво

Військова справа

Генетика

Географія

Геологія

Господарство

Держава

Дім

Екологія

Економетрика

Економіка

Електроніка

Журналістика та ЗМІ

Зв'язок

Іноземні мови

Інформатика

Історія

Комп'ютери

Креслення

Кулінарія

Культура

Лексикологія

Література

Логіка

Маркетинг

Математика

Машинобудування

Медицина

Менеджмент

Метали і Зварювання

Механіка

Мистецтво

Музика

Населення

Освіта

Охорона безпеки життя

Охорона Праці

Педагогіка

Політика

Право

Програмування

Промисловість

Психологія

Радіо

Регилия

Соціологія

Спорт

Стандартизація

Технології

Торгівля

Туризм

Фізика

Фізіологія

Філософія

Фінанси

Хімія

Юриспунденкция

Тема 15. Синтез тригерів

Під час обробки цифрової інформації виникає необхідність у записі двійкових слів і їх тимчасовому зберіганні.

Оскільки двійкове слово - це набір нулів і одиниць, то для зберігання одного розряду цього слова потрібно елемент, який може знаходитися в двох чітко помітних станах, одне з яких трактують як нульове, а другий як одиничне.

В даний час в якості таких елементів використовуються електронні пристрої, відмінною рисою яких є те, що в одному стані напруга на виході цього пристрою відповідає рівню логічного нуля, і цей стан приймають як нульове, а в другому -- рівнем логічної одиниці, і цей стан приймають як одиничне, причому кожне з цих станів стабільно і однаково правомочні.

Для переведення пристрою з одного стану в інший потрібні відповідні керуючі вхідні сигнали. Ці сигнали ми зазвичай трактуємо як сигнали запису нуля або сигнали запису одиниці. Подібні пристрої отримали назву Тригер.

Існує велике різноманіття тригерів. Основна відмінність їх один від одного полягає в характері управління або в способі запису інформації, хоча існує і багато інших класифікацій їх. Найбільш поширення в даний час отримали такі різновиди тригерів, що відрізняються характером управління:

- Найпростіші RS -тригери;

- RS -тригери з керованою записом (шляхом завантаження);

- Найпростіші (прозорі) D -тригера (засувки, фіксатори);

- Синхронні RS -тригери;

- Синхронні D -тригери;

- JK -тригери;

- T -тригери;

Основою побудови будь-якого різновиду тригера є найпростіший RS -тригер.

Найпростішими з послідовнісних цифрових вузлів є тригери – логічні схеми, які можуть знаходитись у одному з двох стійких станів і стрибком переходити в інший стан під впливом зовнішніх сигналів (через це інколи тригер називають бістабільним елементом). Перехід у інший стан частіше за все залежить не тільки від поточних значень вхідних сигналів, але й від попереднього стану тригера. Інформація про попередній стан тригера, що надходить з його виходу разом з вхідними сигналами, визначає його роботу. Саме через це тригери завжди є пристроями із зворотними зв’язками.

У цифровій техніці використовують тригери, побудовані на логічних елементах. Тригери, в свою чергу, є основою для побудови складних функціональних цифрових вузлів різного призначення – лічильників та розподілювачів імпульсів, дільників частоти слідування імпульсів, регістрів, запам'ятовувальних пристроїв.

Інтегральні тригери класифікуються за способом отримання інформації, за принципом побудови та функціональними можливостями.

За способом отримання інформації розрізняють синхронні та асинхронні тригери. Асинхронні тригери сприймають інформаційні сигнали та реагують на них безпосередньо в момент їх появи на інформаційних входах тригера. Синхронні тригери реагують на інформаційні сигнали за умов наявності дозволяючого сигналу на спеціальному керуючому вході С, який називають входом синхронізації. Синхронні тригери у свою чергу поділяються на тригери із статичним та динамічним управлінням по синхровходу.

Тригери із статичним управлінням (керовані рівнем сигналу) сприймають інформаційні сигнали за умови надходження на синхровхід рівня логічної одиниці (прямий С-вхід) або нуля (інверсний С-вхід). Тригери із динамічним управлінням (керовані фронтом сигналу) сприймають інформаційні сигнали при зміні сигналу на С-вході з 0 на 1 (прямий динамічний С-вхід) або з 1 на 0 (інверсний динамічний С-вхід).

За принципом побудови синхронні тригери можна поділити на одноступеневі та двоступеневі. Одноступеневі тригери мають лише один ступінь запам’ятовування інформації, а у двоступеневих тригерах таких ступенів два. Спочатку інформація записується у перший ступінь, потім переноситься у другий і потрапляє на вихід тригера. Двоступеневі тригери також називають тригерами типу MS (від англійського Master – Slave, тобто «майстер – помічник»). Ця абревіатура відображає характер роботи тригера: вхідна ступень виробляє нове значення вихідної змінної Q, а вихідна ступень його копіює.

За функціональними можливостями (або за способом організації логічних зв’язків) розрізняють:

1. Тригер з окремим встановленням станів 0 та 1 (RS-тригер). R (від англійського RESET – скидання) – окремий вхід встановлення у стан 0. S (від англійського SET – встановлення) – окремий вхід встановлення тригера у стан 1.

2. Універсальний тригер з інформаційними входами J та K (JK-тригер). Тут J – вхід для встановлення універсального тригера у стан 1. K – вхід для встановлення універсального тригера у стан 0.

3. Тригер, який отримує інформацію лише через один вхід D – тригер затримки або D-тригер (D від англійського DELAY – затримка). Тут вхід D – інформаційний вхід для встановлення тригера у стан, який співпадає з логічним рівнем на цьому вході.

4. Тригер із лічильним входом – Т-тригер або лічильний тригер. Тут вхід Т – лічильний вхід.

5. Комбіновані тригери, у яких сполучені декілька типів тригерів. Наприклад, тригер типу RST – лічильний тригер, що також має входи встановлення та скидання.

З класифікації тригерів за їх функціональними можливостями стає зрозумілим, що назва тригера за цією ознакою цілком визначається типами його входів. Тригер будь-якого типу має два виходи: прямий Q та інверсний Стан тригера визначається за прямим виходом.

Головними показниками тригерів є їх швидкодія, чутливість, потужність, що споживається від джерела живлення, захищеність від перешкод та функціональні можливості. Швидкодія визначається максимальною частотою перемикань станів тригера і досягає сотень мегагерц. Чутливість тригера визначається найменшою напругою на вході (пороговою напругою), при якій відбувається перемикання тригера. Захищеність тригера від перешкод визначається його спроможністю працювати за умов впливу на нього різноманітних перешкод. Функціональні можливості визначаються кількістю та типом входів тригера.

Для повного визначення тригера достатньо задати його структурну схему на підставі базових логічних елементів (частіше за все використовують елементи ТА-НІ, АБО-НІ) та закон функціонування тригера у вигляді логічної функції або таблиці переходів.

RS-тригери.

Асинхронний RS – тригер з прямими входами.

Вхід R–це вхід скидання тригера в 0 (Reset – скидання).

Вхід S– це вхід встановлення тригера в 1 (Set – встановлення).

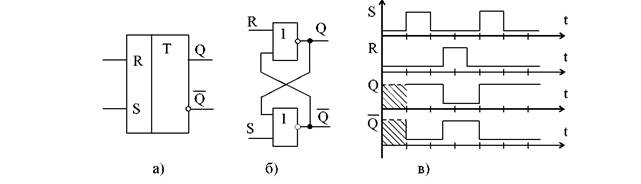

Асинхронним – називається такий тригер, який змінює свій стан в момент подання вхідного сигналу на входи R і S (рис. 15.1). S R T

Рис. 15.1. Асинхронний RS – тригер: а – графічне позначення; б – реалізація на елементах АБО-НЕ; в – часові діаграми роботи.

Таблиця переходів RS – тригера

| Вхід – S | Вхід – R | Вихід –Qi+1 | Режим роботи |

| Qi | Зберігання | ||

| Скидання в 0 | |||

| Встановлення в 1 | |||

| – | Заборонений |

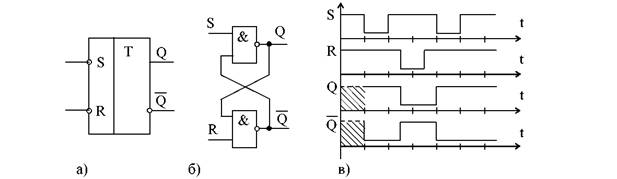

Асинхронний RS-тригер с інверсними входами.

Активним сигналом для такої схеми є логічний 0(рис. 15. 2).

Рис. 15. 2. Асинхронний RS – тригер: а – графічне позначення; б – реалізація на елементах І-НЕ; в – часові діаграми роботи.

Робота тригера визначається таблицею переходів.

Таблиця переходів RS-тригер с інверсними входами

| Вхід – S | Вхід – R | Вихід – Qi+1 | Режим |

| - | Заборонений | ||

| Встановлення в 1 | |||

| Скидання в 0 | |||

| Qi | Зберігання |

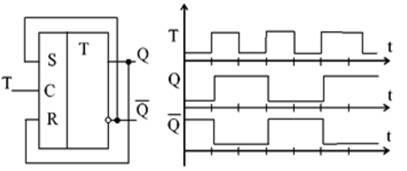

Синхронний RS-тригер.

Тригер називається синхронним, якщо в нього крім, інформаційних входів S і R, є тактовий вхід С.

Синхронний тригер зі статичним керуванням змінює свій стан при логічній 1 на вході С (якщо С вхід прямий) або при логічному 0 на вході С (якщо С вхід інвертований).

Активним сигналом для приведеної схеми (рис. 15.3) є логічна 1.

Таблиця переходів синхронного RS-тригера

| С | S | R | Qi+1 | Режим роботи |

| * | * | Qi | Зберігання | |

| Qi | Зберігання | |||

| Скидання в 0 | ||||

| Встановлення в 1 | ||||

| − | Заборонений |

а) б) в)

Рис. 15.3. Синхронний RS – тригер: а – графічне позначення; б – реалізація на елементах І-НЕ; в – часові діаграми роботи.

Т-тригери.

Асинхронний Т-тригер.

Т – тригер має один інформаційний Т – вхід (від англ. toggle) (рис. 15.4). Зміна стану тригера відбувається кожний раз при зміні вхідного сигналу в визначеному напрямку. Стан Т – тригера визначається його станом в попередньому такті.

Таблиця переходів асинхронного Т-тригера.

| Т | Qi+1 | Режим роботи |

| Qi | Зберігання | |

| Qi | Інверсія |

а) б)

Рис. 15.4. Асинхронний Т – тригер: а – графічне позначення; б – часові діаграми роботи.

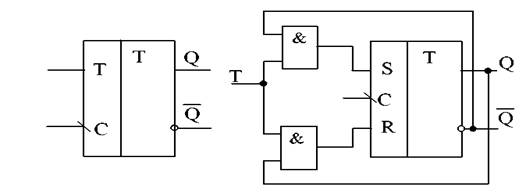

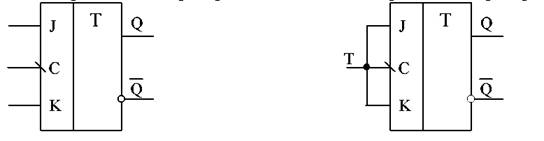

Синхронний Т – тригер.

Синхронний Т – тригер спрацьовує по фронту наростання або спаду інформаційного сигналу (рис. 15.5). При 1 на вході Т, тригер змінює свій стан на протилежний під дією інформаційного сигналу.

Таблиця переходів синхронного Т – тригера

| Т | Qi+1 | Режим роботи |

| Qi | Зберігання | |

| Qi | Інверсія |

а) б)

Рис. 15.5. Синхронний Т – тригер: а – графічне позначення; б – реалізація Т – тригера на базі RS – тригерa;

Рис. 15. 6. Часові діаграми роботи синхронного Т – тригера.

D-тригери.

D – тригери (тригери затримки)на відміну від розглянутих раніше мають один інформаційний вхід D для встановлення в стан 1або 0. Позначення D– це перша буква англ. слова delay – затримка. Функціональна особливість D

– тригерів в тому, що сигнал на виході Q в такті n+1повторює вхідний сигнал

Dn в попередньому такті nі зберігає цей стан до приходу наступного тактового імпульсу. D– тригер затримує на один такт інформацію на вході D(рис. 15. 7).

Таблиця переходів D-тригера.

| Т | Qi+1 | Режим роботи |

| Qi | Зберігання | |

| Qi | Інверсія |

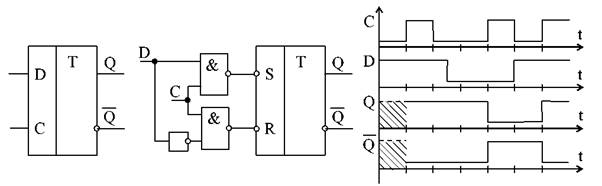

а) б) в)

Рис.15. 7. Синхронний D – тригер: а – графічне позначення; б – реалізація D

– тригера на базі RS – тригера ; в – часові діаграми роботи.

Синхронний D-тригер з асинхронними входами R і S.

Асинхронні входи Rі Sмають пріоритет (тільки при R=1 i S=1 даний тригер буде працювати як синхронний D-тригер) (рис. 15. 8).

Рис. 15. 8. Синхронний D – тригер з асинхронними інвертованими входами RS.

Таблиця переходів синхронного D - тригера

| C | D | S | R | Qi+1 | Режим роботи |

| * | - | Заборонений | |||

| * | Встановлення в 1 | ||||

| * | Скидання в 0 | ||||

| * | Qi | Зберігання | |||

| Скидання в 0 | |||||

| Встановлення в 1 |

JK – тригер.

JK – тригери не мають невизначеного стану. При всіх вхідних комбінаціях, крім однієї Jn = 1, Kn =1 вони працюють, як RS – тригери, при цьому вхід J відповідає входу S, а вхід K відповідає входу R. При вхідній комбінації Jn = 1, Kn = 1 з кожним тактом відбувається зміна вихідного сигналу (режим лічильника).

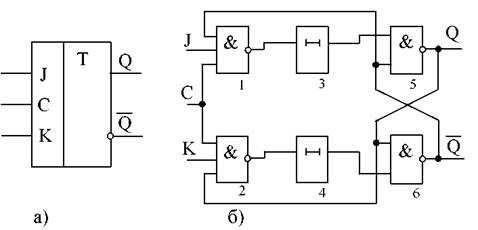

Логічна структура синхронного JK – тригера подана на рис.15.9 б.

Робота JK – тригера описується характеристичним рівнянням:

Qn +1 = Jn ∧ Qn ∨ Kn ∧ Qn.

При Jn = Kn = 0 на виходах елементів 1 і 2 буде q1 =q2 = 1 (незалежно відзначень сигналів Q і Q), це нейтральна комбінація для тригера (елементи 5 і 6), який зберігає записану раніше інформацію. Якщо Jn ≠ Kn вихідний стан тригера буде визначатись логічним елементом 1 або 2, на всіх входах якого логічна 1. Вхідна комбінація Jn = Kn = 1 при будь якому стані тригера викликає зміну (інвертування) вихідного сигналу.

Елементи затримки (3, 4) створюють часовий зсув між моментом вводу вхідної інформації Jn Qn або Kn Qn і початком формування вихідної (Qn +1 і Qn +1). Без цих елементів під час дії вхідної комбінації Jn = Kn =1 почнеться генерація в зв’язку з тим, що з кожною зміною вихідних сигналів на входах присутня комбінація, яка спричиняє зміну вихідного сигналу.

Рис. 15. 9. Синхронний JK – тригер: а – графічне позначення; б – логічна структура JK – тригера.

Таблиця переходів синхронного JK – тригера

| C | D | S | R | Qi+1 | Режим роботи |

| * | - | Заборонений | |||

| * | Встановлення в 1 | ||||

| * | Скидання в 0 | ||||

| * | Qi | Зберігання | |||

| Скидання в 0 | |||||

| Встановлення в 1 |

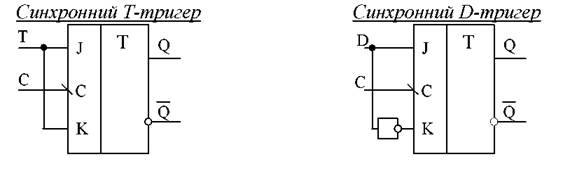

JK – тригери відносяться до універсальних пристроїв, шляхом відповідного з’єднання виводів вони перетворюються в тригери інших типів.

Універсальний JK – тригер можна використовувати як D, T і RS – тригер.

Синхронний RS-тригер Асинхронний Т-тригер

Тема 16. Синтез лічильників

Лічильником називають операційний елемент послідовної дії, що здійснює рахунок імпульсів, які надходять на його вхід. Результат рахунку зберігається лічильником до приходу наступного імпульсу. Зчитування результату рахунку може відбуватися в проміжках між рахунковими імпульсами.

Лічильники, як і зсувні регістри, складаються з ланцюжка послідовно включених тригерів. Розрядність лічильника, а отже, і число тригерів N визначаються максимальним числом, до якого він повинен рахувати. Це число називається коефіцієнтом (модулем) рахунку – Кр. Якщо число вхідних імпульсів n>Кр , то через кожні Кр імпульсів лічильник повертається у вихідний стан і починає рахувати імпульси спочатку.

Велика різномантність типів лічильників викликана їхнім широким використанням як в обчислювальній техніці, так і в різних пристроях автоматики. Вони застосовуються для утворення послідовностей адрес команд, для рахунку числа циклів виконання операцій, для запам'ятовування коду в аналого-цифрових перетворювачах іт.д..

Розглянемо найпоширеніші типи лічильників

Асинхронний (послідовний) двійковий лічильник.

Такий лічильник утворений ланцюжком послідовно ввімкнених лічильних тригерів (рис.16.1). Результат рахунку відображається на виходах лічильника Q(N-1),…, Q0у вигляді паралельного двійкового коду числа порахованих імпульсів. Оскільки число вихідних змінних дорівнює числу тригерів N і кожна змінна може приймати лише два значення, то число можливих станів (коефіцієнт рахунку) дорівнює: Kp=2N. Тому що з 2N станів одне доводиться на нульовий стан, то максимальне число, при якому лічильник повністю заповнюється одиницями, дорівнює (2N -1).

Найпростішим однорозрядним лічильником з Kp=2 є Т-Тригер, що міняє свій стан на протилежний під дією кожного вхідного сигналу. У результаті перепаду на пруги на виході тригери мають удвічі меншу частоту, ніж на вході. По цих перепадах запускається наступний тригер, і на його виході зміни стану відбуваються вже в чотири рази рідше, ніж на вході першого тригера.

Рис.16.1.

З приходом кожного наступного імпульсу паралельний двійковий код на виході лічильника буде збільшуватися на одиницю, поки не наступить переповнення лічильника, при якому всі тригери скинуться в нульовий стан.

Істинна інформація на виходах лічильника встановлюється тільки через час N-1, що пройшов після надходження тактового імпульсу. Де t - затримка поширення імпульсу в кожному тригері. При подальшому збільшенні розрядності, сумарна затримка може привести до спотворювання інформації в лічильнику. Тому багато-розрядні лічильники з послідовним переносом рахункових імпульсів від тригера до тригера можуть працювати тільки на знижених частотах, при досить великих періодах проходження імпульсів.

Крім розглянутого підсумовуючого лічильника, є й лічильники, що віднімають, у яких вихідний код зменшується на 1 із приходом кожного рахункового імпульсу. Такий лічильник отримується при подачі інверсних сигналів на тактові входи. Для цього необхідно тактові входи тригерів підключити до інверсних виходів Q попередніх тригерів.

Синхронний (паралельний) двійковий лічильник.

Паралельні лічильники (рис.16.2) мають максимальну швидкодію, оскільки в них усі розряди переключаються одночасно. Паралельний лічильник містить розрядні тригери з кон'юнкторами, що аналізують стан попередніх розрядів. При надходженні вхідного сигналу переключаються тільки ті тригери, для яких усі попередні були в одиничному стані.

Час установки лічильника не залежить від розрядності і дорівнює

Рис.16.2.

де - затримка сигналу кон'юнктором.

t - затримка поширення імпульсу в тригері.

Труднощі реалізації багаторозрядних паралельних лічильників пов'язані з ростом числа входів у кон'юнкторів по мірі збільшення розрядності лічильника. Другий обмежуючий фактор - ріст навантаження на виходи тригерів по мірі збільшення числа розрядів лічильника. Застосування різних схем буферного типу для подолання зазначених обмежень небажано, тому що знижується швидкодія лічильника.

У паралельних лічильниках всі розряди переключаються одночасно, тому їхній структурі властиві тимчасові змагання сигналів. При використанні двоступінчастих тригерів ці недоліки виключаються.

Реверсивні лічильники.

Реверсивні лічильники змінюють напрямок рахунку під впливом керуючого сигналу чи при зміні точки подачі лічильних сигналів. У першому випадку схема має рахунковий і лічильний входи, у другому - два лічильних входи.

Найбільш розповсюджений спосіб побудови реверсивних лічильників - переключення міжрозрядних зв'язків. Лічильники прямого і зворотного рахунку розрізняються лише точкою знімання сигналу, який подається з попереднього розряду на наступний. Якщо керуючий сигнал перебудовує міжрозрядні зв'язки, переносячи точку знімання сигналу з одного виходу тригера на іншій, то реалізується схема реверсивного лічильника.

Послідовний лічильник перетвориться в реверсивний шляхом введення в його структуру елементів реверса. У зв'язку з появою додаткових затримок введення реверса знижується швидкодія лічильника.

Рис.16.3.

Лічильник з довільним коефіцієнтом рахунку.

Часто потрібні лічильники із числом стійких станів, відмінних від 2N. Наприклад, в електронних годинниках є мікросхеми з коефіцієнтами рахунку 6 (десятки хвилин), 10 (одиниці хвилин), 7 (дні тижня), 24 (години). Для побудови лічильника з Кp не рівним 2N можна використовувати пристрій з N-тригерів, для якого виконується умова 2N >Кp . Очевидно, такий лічильник має зайві стійкі стани (2N-Кp). Виключити ці непотрібні стани можна використанням зворотних зв'язків, по ланцюгах яких лічильник перемикається в нульовий стан у тому такті роботи, у якому він дораховує до числа Кр

Для лічильника з К =10 потрібні чотири тригери (тому що 23<10<24). Лічильник повинен мати десять стійких станів (0,..., 9). У тому такті, коли він повинен був би перейти в одинадцятий стійкий стан (число 10), його необхідно встановити у вихідний нульовий стан. Для такого лічильника можна використовувати будь-який чотирирозрядний лічильник з зворотнім зв'язком з виходів, що відповідають числу 10 (тобто 2 і 8), на входи установки лічильника в 0. На самому початку одинадцятого стану (число 10) на обох входах елемента І мікросхеми з'являються логічні 1, що виробляють сигнал скидання всіх тригерів лічильника в нульовий стан.

Розглянутий лічильник є двійковим еквівалентом рахункової декади, що представляє будь-яку десяткову цифру її двійковим кодом. Тому такий лічильник називають двійково-десятковим, а його вихідний код - двійково-десятковим кодом (або кодом8421).

Якщо двійково-десятковий лічильник призначений для роботи в системах, де потрібна візуальна інформація про число підрахованих імпульсів (наприклад, різні цифрові вимірювальні прилади), то після лічильника ставиться перетворювач двійково-десяткового коду в код семисегментного індикатора.

Лічильник з попередньою установкою.

Лічильник може встановлюватися в початковий стан, рівний будь-якому числу від 0 до Кp-1. Ця операція здійснюється паралельним записом у лічильник коду необхідного числа. Рахунок (додавання або вирахування) буде починатися вже не з нуля, і а із встановленого числа. Такий режим роботи лічильника необхідний, команд із заданої початкової адреси.

Лічильники з попередньою установкою, звичайно, є універсальними й можуть працювати в режимах додавання, віднімання, установки заданого коду, установки (скидання) нуля.

Дільники частоти.

Лічильники можуть виконувати функції дільників частоти, тобто пристроїв, що формують із імпульсної послідовності із частотою і" імпульсну послідовність на виході останнього тригера із частотою ґ , в К раз меншу за вхідний. При такому використанні лічильників не потрібно знати, яке число в ньому записано в даний момент; тому дільники можуть не мати всіх проміжних виходів. Це значно спрощує їхню схему й конструкцію.

Читайте також:

- Аеробний механізм ресинтезу АТФ

- Аналіз і синтез.

- Аналіз та синтез моделей систем

- Апертурний синтез

- Аферентний синтез та зворотна аферентація

- БІОСИНТЕЗ АМІНОКИСЛОТ

- Біосинтез білка

- Біосинтез білку.

- Біосинтез гліцерину

- БІОСИНТЕЗ ЖИРНИХ КИСЛОТ

- Біосинтез жирних кислот

- Біосинтез ізопреноїдів і локалізація ефірних олій в рослинах.

| <== попередня сторінка | | | наступна сторінка ==> |

| Тема 14. Синтез суматорів | | | Пример 2 |

|

Не знайшли потрібну інформацію? Скористайтесь пошуком google: |

© studopedia.com.ua При використанні або копіюванні матеріалів пряме посилання на сайт обов'язкове. |