РЕЗОЛЮЦІЯ: Громадського обговорення навчальної програми статевого виховання

ЧОМУ ФОНД ОЛЕНИ ПІНЧУК І МОЗ УКРАЇНИ ПРОПАГУЮТЬ "СЕКСУАЛЬНІ УРОКИ"

ЕКЗИСТЕНЦІЙНО-ПСИХОЛОГІЧНІ ОСНОВИ ПОРУШЕННЯ СТАТЕВОЇ ІДЕНТИЧНОСТІ ПІДЛІТКІВ

Батьківський, громадянський рух в Україні закликає МОН зупинити тотальну сексуалізацію дітей і підлітків

Відкрите звернення Міністру освіти й науки України - Гриневич Лілії Михайлівні

Представництво українського жіноцтва в ООН: низький рівень культури спілкування в соціальних мережах

Гендерна антидискримінаційна експертиза може зробити нас моральними рабами

ЛІВИЙ МАРКСИЗМ У НОВИХ ПІДРУЧНИКАХ ДЛЯ ШКОЛЯРІВ

ВІДКРИТА ЗАЯВА на підтримку позиції Ганни Турчинової та права кожної людини на свободу думки, світогляду та вираження поглядів

- Гідрологія і Гідрометрія

- Господарське право

- Економіка будівництва

- Економіка природокористування

- Економічна теорія

- Земельне право

- Історія України

- Кримінально виконавче право

- Медична радіологія

- Методи аналізу

- Міжнародне приватне право

- Міжнародний маркетинг

- Основи екології

- Предмет Політологія

- Соціальне страхування

- Технічні засоби організації дорожнього руху

- Товарознавство продовольчих товарів

Тлумачний словник

Авто

Автоматизація

Архітектура

Астрономія

Аудит

Біологія

Будівництво

Бухгалтерія

Винахідництво

Виробництво

Військова справа

Генетика

Географія

Геологія

Господарство

Держава

Дім

Екологія

Економетрика

Економіка

Електроніка

Журналістика та ЗМІ

Зв'язок

Іноземні мови

Інформатика

Історія

Комп'ютери

Креслення

Кулінарія

Культура

Лексикологія

Література

Логіка

Маркетинг

Математика

Машинобудування

Медицина

Менеджмент

Метали і Зварювання

Механіка

Мистецтво

Музика

Населення

Освіта

Охорона безпеки життя

Охорона Праці

Педагогіка

Політика

Право

Програмування

Промисловість

Психологія

Радіо

Регилия

Соціологія

Спорт

Стандартизація

Технології

Торгівля

Туризм

Фізика

Фізіологія

Філософія

Фінанси

Хімія

Юриспунденкция

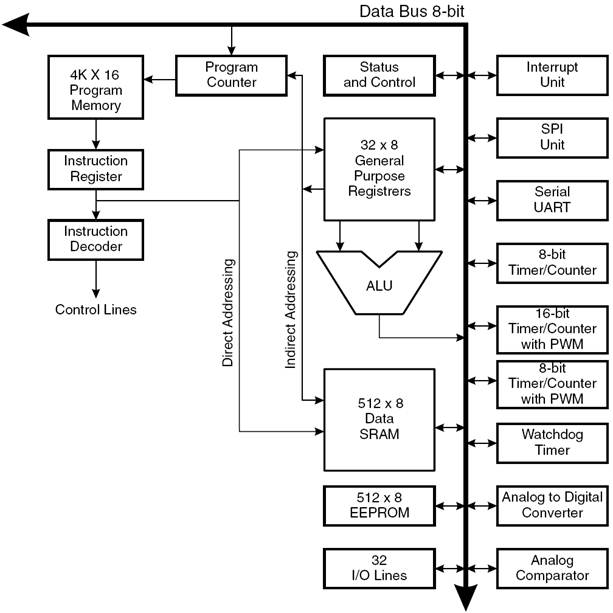

Огляд архітектури AT90S8535

Укрупнену|укрупняна| структурну схему мікроконтролера AT90S8535 приведено на рис.4.1. Мікроконтролер має 32 8-розрядних регістри|реєстру| загального|спільного| призначення, їх ще називають регістровим файлом. Доступ до цих регістрів|реєстрів| здійснюється за один машинний цикл. Тому за один машинний цикл виконується одна операція АЛП|. Два операнди вибираються з|із| регістрового файлу, виконується операція, результат її записується|занотовується| в регістровий файл - все за один машинний цикл.

Шість із|із| 32 регістрів|реєстрів| (R26-R31) можна використовувати як три 16-розрядні покажчики в адресному просторі даних, що дає можливість|спроможність| використовувати високоефективну адресну арифметику. З|із| цими регістровими парами можна працювати як з|із| 16-розрядними регістрами|реєстрами|, які називатимуться X (R26, R27), Y (R28, R29) і Z (R30, R31). Регістр|реєстр| Z можна також використовувати для адресації таблиць в пам'яті програм.

Рис.4.1 – Архітектура AT90S8535

АЛП підтримує арифметичні й логічні операції з регістрами, з константами й регістрами. Операції над окремими регістрами також виконуються в АЛП.

Крім|крім| регістрових операцій, для роботи з|із| регістровим файлом можуть використовуватися доступні режими адресації, оскільки регістровий файл займає|позичає,посідає| адреси $00-$1F у області даних (SRAM), звертатися|обертатися| до них можна як до елементів пам'яті.

У просторі введення-виведення 64 адреси відведено для периферійних пристроїв, таких як керуючі регістри, таймери/лічильники та ін. Доступ до простору введення-виведення може здійснюватися безпосередньо, як до комірок пам'яті (SRAM), розташованих після регістрового файлу ($20-$5F).

Процесори AVR побудовані по гарвардській архітектурі з роздільними областями пам'яті програм і даних. Доступ до пам'яті програм здійснюється за допомогою однорівневого буфера. Під час виконання команди, наступна вибирається з пам'яті програм. Подібна концепція дає можливість виконувати по одній команді за кожний машинний цикл. Пам'ять програм - це внутрісистемна завантажувана FLASH-память.

За допомогою команд відносних переходів і виклику підпрограм здійснюється доступ до всього адресного простору. Більша частина команд AVR має розмір 16-розрядів, одне слово. Кожна адреса в пам'яті програм містить одну 16- або 32-розрядну команду.

При обробці переривань і виклику підпрограм адреса повернення запам'ятовується в стеку. Стек розміщується в пам'яті даних загального|спільного| призначення, відповідно розмір стека обмежений тільки|лише| розміром доступної пам'яті даних і її використанням в програмі. Всі програми користувача повинні ініціалізувати покажчик стека (SP) в програмі, що виконується після|потім| скидання|скиду| (до того, як викликаються|спричиняються| підпрограми і дозволяються переривання). 8-розрядний покажчик стека доступний для читання/запису у області введення/виведення.

Доступ до 512 байтів статичного ОЗУ, регістрового файла та регістрів введення/виведення здійснюється за допомогою п'яти доступних режимів адресації, які підтримуються архітектурою AVR.

Весь простір пам'яті AVR є лінійним і безперервним.

Гнучкий модуль переривань має власний керуючий регістр у просторі введення/виведення і прапорець глобального дозволу переривань у регістрі стану. Кожному перериванню призначено свій вектор у початковій області пам'яті програм. Різні переривання мають пріоритет відповідно до розташування їхніх векторів. За молодшими адресами розташовані вектори з більшим пріоритетом.

Читайте також:

- II. Відкриття і подолання схоластичного світогляду

- VII. Рекомендації щодо безпечного проведення ремонту та технічного огляду сільськогосподарської техніки

- Аналіз оглядових рентгенограм при перитоніті

- Аналіз оглядових рентгенограм при перфорації порожнинного органу

- Аналітичний огляд

- АНАЛІТИЧНИЙ ОГЛЯД

- Аналітичний огляд використання вторинної сировини і відходів

- Античній світогляд

- Архітектури систем управління мережами

- В яких випадках роботодавець зобов'язаний забезпечити за свій рахунок позачерговий медичний огляд працівників?

- В якій послідовності проводиться огляд трупа?

- Види світогляду: міфологічний, релігійний та філософський (натуралістична, об’єктивно-ідеалістична, субєктивно-ідеалістичні і матеріалістичні моделі).

| <== попередня сторінка | | | наступна сторінка ==> |

| Кварцовий генератор | | | Файл регістрів загального призначення |

|

Не знайшли потрібну інформацію? Скористайтесь пошуком google: |

© studopedia.com.ua При використанні або копіюванні матеріалів пряме посилання на сайт обов'язкове. |